# CSE 315 Microprocessors & Microcontrollers

#### Tanvir Ahmed Khan

Department of Computer Science and Engineering Bangladesh University of Engineering and Technology.

October 21, 2014

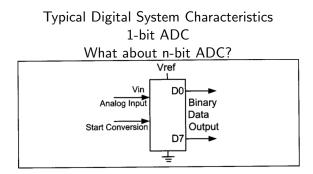

#### **ADC Basics**

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

# ADC Jargons

- Sampling

- Quantization

- Resolution/Step Size

- Conversion Time

- ► V<sub>ref</sub>

- Digital Data Output

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

# Resolution/Step Size

•

$$n = 8, V_{ref} = 2.56V$$

•

$$n = 10, V_{ref} = 2.56V$$

#### Digital Data Output

# Analog-to-Digital Conversion Technologies

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

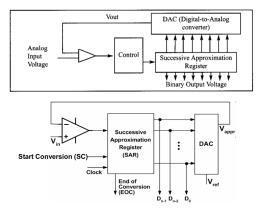

- Successive Approximation

- Integration

- Counter Based Conversion

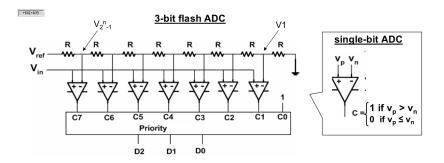

- Parallel Conversion

- ► Flash ADC

#### Successive Approximation ADC

◆□▶ ◆□▶ ◆豆▶ ◆豆▶ ̄豆 \_ のへぐ

#### Flash ADC

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

#### ADC Programming in C

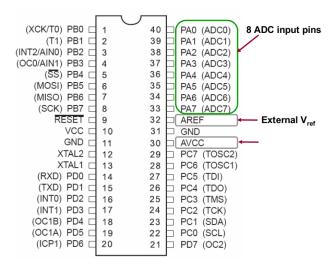

#### ATmega16/32 ADC Relevant Pin Diagram

- 4 日 2 4 日 2 4 日 2 4 日 2 9 9 9 9 9

◆□ ▶ < 圖 ▶ < 圖 ▶ < 圖 ▶ < 圖 • 의 Q @</p>

▶ 10-bit ADC

- 10-bit ADC

- 2 output registers,

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

- 10-bit ADC

- 2 output registers,

- ► ADCH:ADCL

- ▶ 16-bits, 6-bits are unused

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

8 Analog input channels,

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ・ ヨ ・ の Q ()

- 8 Analog input channels,

- 7 differential input

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

V<sub>ref</sub> options,

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ▶ Analog V<sub>cc</sub>, 5V

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ▶ Analog V<sub>cc</sub>, 5V

- internal 2.56V

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ► Analog V<sub>cc</sub>, 5V

- ▶ internal 2.56V

- external AREF pin

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ► Analog V<sub>cc</sub>, 5V

- internal 2.56V

- external AREF pin

- ADC clock rate != MCU CPU clock rate

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ▶ Analog V<sub>cc</sub>, 5V

- internal 2.56V

- external AREF pin

- ADC clock rate != MCU CPU clock rate

selection of pre-scaler

- 10-bit ADC

- 2 output registers,

- ADCH:ADCL

- 16-bits, 6-bits are unused

- Option to adjust left or right

- 8 Analog input channels,

- 7 differential input

- with optional gain of 10x & 200x

- However, only one conversion at a time

- V<sub>ref</sub> options,

- ► Analog V<sub>cc</sub>, 5V

- internal 2.56V

- external AREF pin

- ADC clock rate != MCU CPU clock rate

- selection of pre-scaler

- AD Conversion takes at-least 13 ADC clock cycles

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

Major Relevant registers

Major Relevant registers

Major Relevant registers

ADCH: ADCL

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

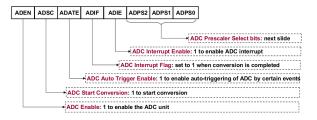

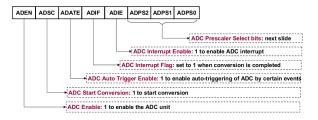

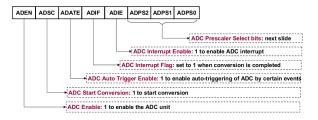

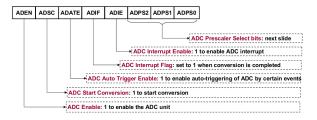

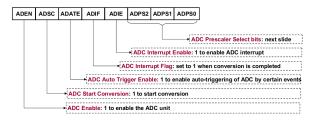

ADCSRA

Major Relevant registers

ADCH: ADCL

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

- ADCSRA

- ADMUX

Major Relevant registers

ADCH: ADCL

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

- ADCSRA

- ADMUX

- SFIOR

Major Relevant registers

► ADCH:ADCL

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

- ADCSRA

- ADMUX

- ► SFIOR

◆□ > ◆□ > ◆臣 > ◆臣 > ─ 臣 ─ のへ(?)

| ADPS2 | ADPS1 | ADPS0 | ADC Clock |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | Reserved  |

| 0     | 0     | 1     | CK/2      |

| 0     | 1     | 0     | CK/4      |

| 0     | 1     | 1     | CK/8      |

| 1     | 0     | 0     | CK/16     |

| 1     | 0     | 1     | CK/32     |

| 1     | 1     | 0     | CK/64     |

| 1     | 1     | 1     | CK/128    |

ADPS2 ADPS1 ADPS0 ADC Clock 0 0 0 Reserved 0 0 1 CK/2 0 1 0 CK/4 0 1 1 CK/8 0 0 CK/16 0 1 CK/32 1 0 CK/64 1 CK/128

#### Initialization,

| ADPS2 | ADPS1 | ADPS0 | ADC Clock |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | Reserved  |

| 0     | 0     | 1     | CK/2      |

| 0     | 1     | 0     | CK/4      |

| 0     | 1     | 1     | CK/8      |

| 1     | 0     | 0     | CK/16     |

| 1     | 0     | 1     | CK/32     |

| 1     | 1     | 0     | CK/64     |

| 1     | 1     | 1     | CK/128    |

- Initialization,

- Polling, ADCSRA = 0b10000001;

| ADPS2 | ADPS1 | ADPS0 | ADC Clock |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | Reserved  |

| 0     | 0     | 1     | CK/2      |

| 0     | 1     | 0     | CK/4      |

| 0     | 1     | 1     | CK/8      |

| 1     | 0     | 0     | CK/16     |

| 1     | 0     | 1     | CK/32     |

| 1     | 1     | 0     | CK/64     |

| 1     | 1     | 1     | CK/128    |

- Initialization,

- Polling, ADCSRA = 0b10000001;

- Interrupt, ADCSRA = 0b10001001;

| ADPS2 | ADPS1 | ADPS0 | ADC Clock |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | Reserved  |

| 0     | 0     | 1     | CK/2      |

| 0     | 1     | 0     | CK/4      |

| 0     | 1     | 1     | CK/8      |

| 1     | 0     | 0     | CK/16     |

| 1     | 0     | 1     | CK/32     |

| 1     | 1     | 0     | CK/64     |

| 1     | 1     | 1     | CK/128    |

- Initialization,

- Polling, ADCSRA = 0b10000001;

- Interrupt, ADCSRA = 0b10001001;

Conversion Start,

| ADPS2 | ADPS1 | ADPS0 | ADC Clock |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | Reserved  |

| 0     | 0     | 1     | CK/2      |

| 0     | 1     | 0     | CK/4      |

| 0     | 1     | 1     | CK/8      |

| 1     | 0     | 0     | CK/16     |

| 1     | 0     | 1     | CK/32     |

| 1     | 1     | 0     | CK/64     |

| 1     | 1     | 1     | CK/128    |

- Initialization,

- Polling, ADCSRA = 0b10000001;

- Interrupt, ADCSRA = 0b10001001;

- Conversion Start,

- ADCSRA = ADCSRA | Ob01000000;

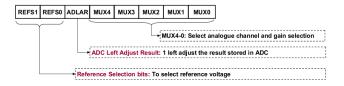

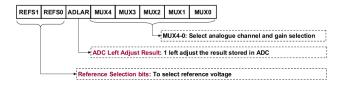

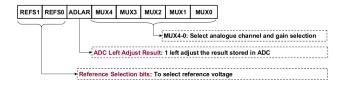

#### ADC Programming ADMUX Register

#### ADC Programming ADMUX Register

| REFS1 | REFS0 | V <sub>ref</sub> |                               |

|-------|-------|------------------|-------------------------------|

| 0     | 0     | AREF pin         | Set externally                |

| 0     | 1     | AVCC pin         | Same as VCC                   |

| 1     | 0     | Reserved         |                               |

| 1     | 1     | Internal 2.56 V  | Fixed regardless of VCC value |

#### Table 13-4: V<sub>ref</sub> Source Selection Table for AVR

#### ADC Programming ADMUX Register

| REFS1 | REFS0 | V <sub>ref</sub> |                               |

|-------|-------|------------------|-------------------------------|

| 0     | 0     | AREF pin         | Set externally                |

| 0     | 1     | AVCC pin         | Same as VCC                   |

| 1     | 0     | Reserved         |                               |

| 1     | 1     | Internal 2.56 V  | Fixed regardless of VCC value |

| Left-Justified               | ADCH                    | ADCL                    |

|------------------------------|-------------------------|-------------------------|

| ADLAR = 1                    | D9 D8 D7 D6 D5 D4 D3 D2 | D1 D0 UNUSED            |

| ADLAR = 0<br>Right-Justified | UNUSED D9 D8            | D7 D6 D5 D4 D3 D2 D1 D0 |

Table 13-4: V<sub>ref</sub> Source Selection Table for AVR

# Sample ADC Program Polling

```

2

3 #include <avr/io.h>

4

5 int main(void)

6 {

7

ADCSRA = 0b10000001:

ADMUX = 0b11100000;

8

9

10

DDRA = DDRB = 0b111111111;

11

while(1)

12

13

{

14

ADCSRA = ADCSRA | 0b01000000:

15

while((ADCSRA & Ob00010000) == 0){}

16

PORTA = ADCH;

17

PORTB = ADCL;

18

}

19

20

return 0;

21 }

```

# Sample ADC Program

Interrupt

```

2

3 #include <avr/io.h>

4 #include <avr/interrupt.h>

5

6 ISR(ADC_vect)

7 {

8

PORTA = ADCH;

PORTB = ADCL:

9

10

ADCSRA = ADCSRA | 0b01000000:

11 }

12

13 int main(void)

14 {

15

ADCSRA = 0b10001001;

16

ADMUX = 0b11100000;

17

18

DDRA = DDRB = 0b11111111:

19

sei();

20

ADCSRA = ADCSRA | 0b01000000;

21

22

while(1)

23

1

24

25

26

return 0:

27 }

```

▲□▶ ▲圖▶ ★ 国▶ ★ 国▶ - 国 - のへで

#### Reference

► The avr microcontroller & embedded system, Chapter 13

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

- Muhammad Ali Mazidi

- Sarmad Naimi

- Sepehr Naimi