## CSE 305: Computer Architecture

Tanvir Ahmed Khan takhandipu@gmail.com

Department of Computer Science and Engineering Bangladesh University of Engineering and Technology.

November 8, 2015

# Recap

| 0        | rs                                       | rt                                                               |                                                                                                       | rd      | shar  | nt    | funct       |

|----------|------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|-------|-------|-------------|

| 31:26    | 25:21                                    | 20:16                                                            | 1                                                                                                     | 5:11    | 10:0  | 6     | 5:0         |

| 35 or 43 | rs                                       | rt                                                               |                                                                                                       | address |       |       |             |

| 31:26    | 25:21                                    | 20:16                                                            | $\langle \  $                                                                                         |         |       |       | 1           |

| 4        | rs                                       | rt                                                               |                                                                                                       | address |       |       |             |

| 31:26    | 25:21                                    | 20:16                                                            | \                                                                                                     | 15:0    |       | 5:0   | 1           |

|          | $\overline{}$                            |                                                                  |                                                                                                       | //      |       |       | 11          |

| opcode   | always                                   | read,                                                            |                                                                                                       |         |       |       | sign-extend |

|          | read                                     |                                                                  |                                                                                                       |         |       |       | and add     |

|          | 31:26<br>35 or 43<br>31:26<br>4<br>31:26 | 31:26 25:21<br>35 or 43 rs<br>31:26 25:21<br>4 rs<br>31:26 25:21 | 31:26 25:21 20:16  35 or 43 rs rt  31:26 25:21 20:16  4 rs rt  31:26 25:21 20:16  opcode always read, | 31:26   | 31:26 | 31:26 | 31:26       |

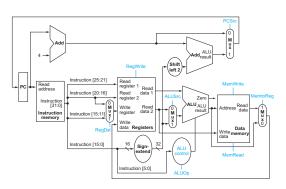

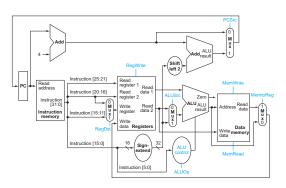

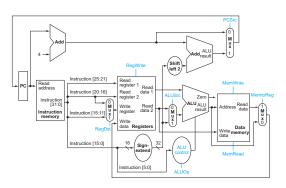

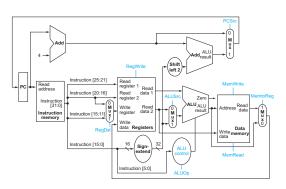

# Today's Topic

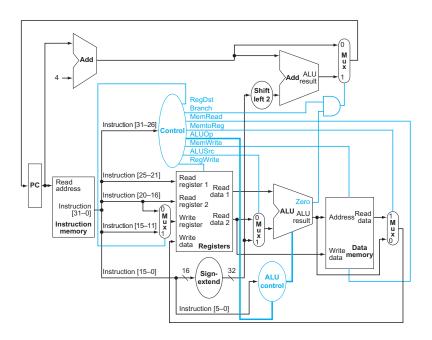

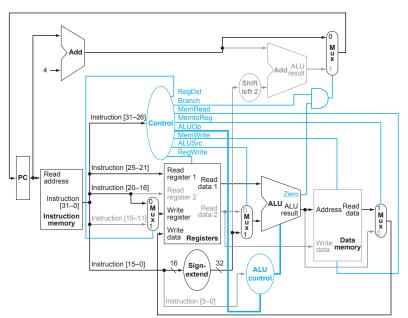

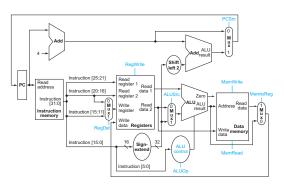

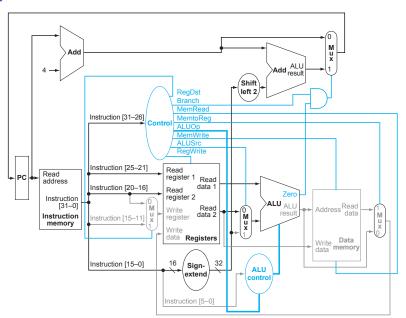

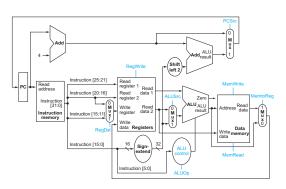

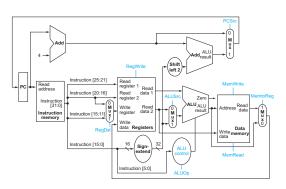

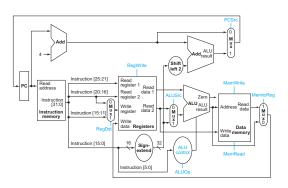

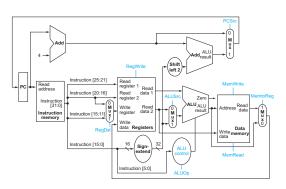

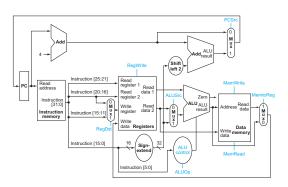

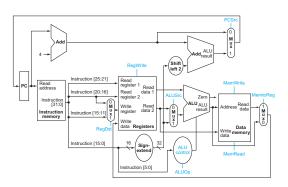

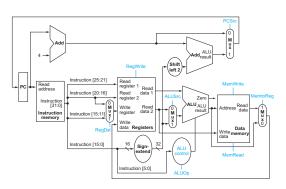

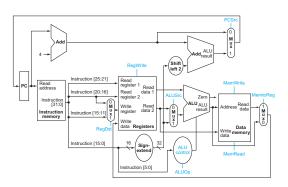

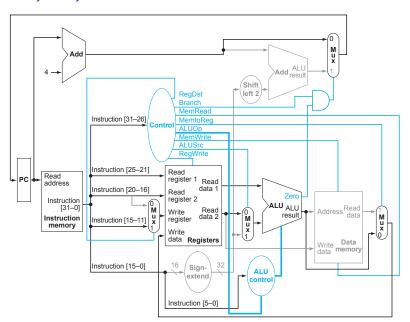

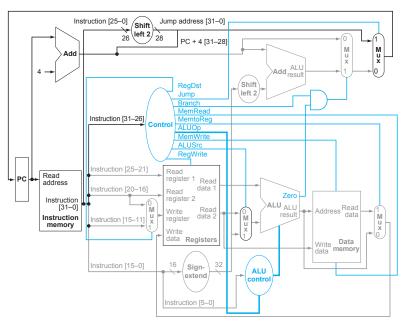

Control Unit

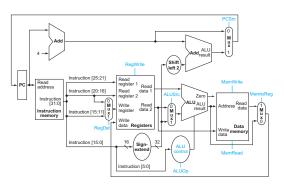

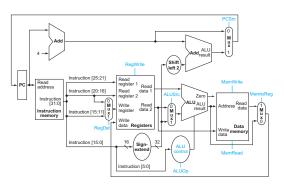

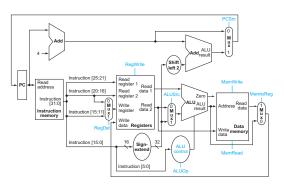

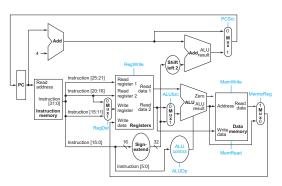

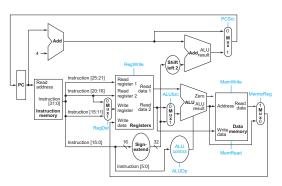

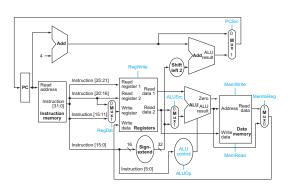

# Control Signal Summary

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address = rd                      |

| RegWrite       | -                                | Write register                                   |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | -                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

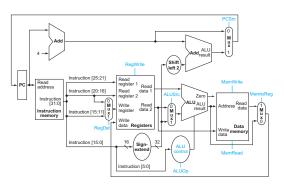

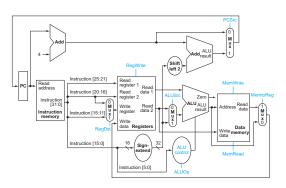

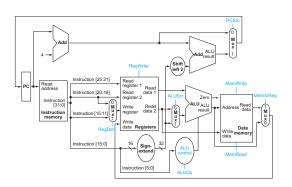

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw |        |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |

| RegWrite       | -                                | Write register                                   |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | -                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        | 1      |       |         |          |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |

| RegWrite       | -                                | Write register                                   |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | =                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        | 1      | 0     |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        | 1      | 0     | 1       |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        | 1      | 0     | 1       | 0        |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| lw | 0      | 1        | 1      | 0     | 1       | 0        | 1        |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

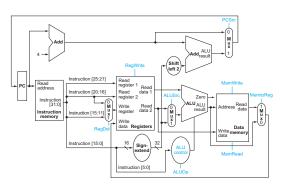

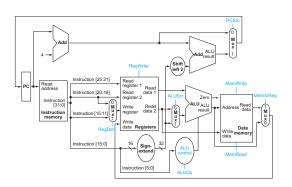

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| sw |        |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address = rd                      |

| RegWrite       | Write - Write register           |                                                  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | =                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address = rd                      |

| RegWrite       | Write - Write register           |                                                  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | =                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      | 0        |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      | 0        | 1      |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      | 0        | 1      | 0     |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      | 0        | 1      | 0     | 0       |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite -     |                                  | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| SW | ×      | 0        | 1      | 0     | 0       | 1        |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite -     |                                  | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|    | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|----|--------|----------|--------|-------|---------|----------|----------|

| sw | ×      | 0        | 1      | 0     | 0       | 1        | X        |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beg |        |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beq | ×      |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |   |

|-----|--------|----------|--------|-------|---------|----------|----------|---|

| beg | X      | 0        |        |       |         |          |          | ı |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beq | ×      | 0        | 0      |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beq | ×      | 0        | 0      | 1     |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |   |

|-----|--------|----------|--------|-------|---------|----------|----------|---|

| beg | X      | 0        | 0      | 1     | 0       |          |          | Ĺ |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beg | X      | 0        | 0      | 1     | 0       | 0        |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |

| RegWrite       | -                                | Write register                                   |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | -                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| beq | ×      | 0        | 0      | 1     | 0       | 0        | ×        |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

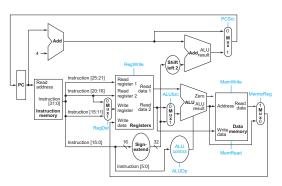

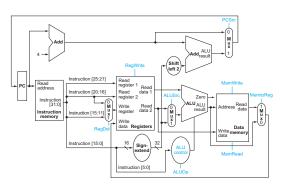

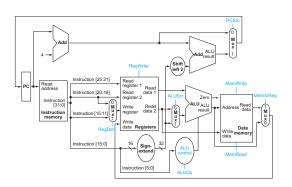

#### add rd, rs, rt

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add |        |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |

|----------------|----------------------------------|--------------------------------------------------|

| RegDst         | Write register address = rt      | Write register address = rd                      |

| RegWrite       | Write - Write register           |                                                  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | -                                | Read data from memory                            |

| MemWrite       | -                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

#### add rd, rs, rt

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite -     |                                  | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        |        |       |         |          |          |

| Control Signal                        | 0                                | 1                                                |  |  |

|---------------------------------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst                                | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite                              | -                                | Write register                                   |  |  |

| AluSrc                                | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc                                 | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead                               | -                                | Read data from memory                            |  |  |

| MemWrite -                            |                                  | Write data into memory                           |  |  |

| MemtoReg Register Write Data from ALU |                                  | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        | 0      |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite -     |                                  | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        | 0      | 0     |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | =                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        | 0      | 0     | 0       |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        | 0      | 0     | 0       | 0        |          |

| Control Signal                        | 0                                | 1                                                |  |  |

|---------------------------------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst                                | Write register address = rt      | Write register address $=$ rd                    |  |  |

| RegWrite                              | -                                | Write register                                   |  |  |

| AluSrc                                | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc                                 | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead                               | -                                | Read data from memory                            |  |  |

| MemWrite                              | -                                | Write data into memory                           |  |  |

| MemtoReg Register Write Data from ALU |                                  | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| add | 1      | 1        | 0      | 0     | 0       | 0        | 0        |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub |        |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                               |  |  |

|----------------|----------------------------------|-------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                     |  |  |

| RegWrite       | -                                | Write register                                  |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instructio |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                |  |  |

| MemRead        | =                                | Read data from memory                           |  |  |

| MemWrite       | =                                | Write data into memory                          |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory            |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      |          |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        |        |       |         |          |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        | 0      |       |         |          |          |

| Control Signal | 0                                | 1                                               |  |  |

|----------------|----------------------------------|-------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                     |  |  |

| RegWrite       | -                                | Write register                                  |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instructio |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                |  |  |

| MemRead        | =                                | Read data from memory                           |  |  |

| MemWrite       | =                                | Write data into memory                          |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory            |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        | 0      | 0     |         |          |          |

| C . I.C: I     |                                  |                                                  |

|----------------|----------------------------------|--------------------------------------------------|

| Control Signal | U                                | 1                                                |

| RegDst         | Write register address = rt      | Write register address $=$ rd                    |

| RegWrite       | -                                | Write register                                   |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |

| MemRead        | =                                | Read data from memory                            |

| MemWrite       | =                                | Write data into memory                           |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        | 0      | 0     | 0       |          |          |

| Control Signal | 0                                | 1                                                |  |  |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |  |  |

| RegWrite       | -                                | Write register                                   |  |  |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        | 0      | 0     | 0       | 0        |          |

| Control Signal | 0                                | 1                                                |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |

| RegWrite       | -                                | Write register                                   |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |

| MemRead        | -                                | Read data from memory                            |  |  |

| MemWrite       | -                                | Write data into memory                           |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |

|     | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|-----|--------|----------|--------|-------|---------|----------|----------|

| sub | 1      | 1        | 0      | 0     | 0       | 0        | 0        |

| Control Signal | 0                                | 1                                                |  |  |  |  |

|----------------|----------------------------------|--------------------------------------------------|--|--|--|--|

| RegDst         | Write register address = rt      | Write register address = rd                      |  |  |  |  |

| RegWrite       | -                                | Write register                                   |  |  |  |  |

| AluSrc         | ALU Second Operand = Read data 2 | ALU Second Operand = lower 16-bit of instruction |  |  |  |  |

| PCSrc          | PC=PC+4                          | PC=branch target                                 |  |  |  |  |

| MemRead        | =                                | Read data from memory                            |  |  |  |  |

| MemWrite       | =                                | Write data into memory                           |  |  |  |  |

| MemtoReg       | Register Write Data from ALU     | Register Write Data from data memory             |  |  |  |  |

#### (add/sub/AND/OR/slt) rd, rs, rt

|         | RegDst | RegWrite | ALUSrc | PCSrc | MemRead | MemWrite | MemtoReg |

|---------|--------|----------|--------|-------|---------|----------|----------|

| rFormat | 1      | 1        | 0      | 0     | 0       | 0        | 0        |

# Arithmetic Logic Unit: ALU

| А                     | LU C  | Contro | ol    | Operation |

|-----------------------|-------|--------|-------|-----------|

| <i>S</i> <sub>3</sub> | $S_2$ | $S_1$  | $S_0$ | Operation |

| 0                     | 0     | 0      | 0     | AND       |

| 0                     | 0     | 0      | 1     | OR        |

| 0                     | 0     | 1      | 0     | ADD       |

| 0                     | 1     | 1      | 0     | SUBTRACT  |

| 0                     | 1     | 1      | 1     | SLT       |

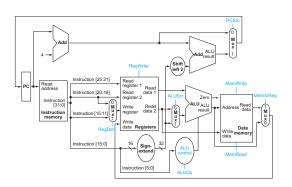

## ALU for different instructions

```

lw rt, 0(rs) ↔ rt ← [rs+4*0],

sw rt, x(rs) ↔ [rs+4*x] ← rt,

beq rs, rt, rd ↔ zero ← (rs-rt == 0)

add rs, rt, rd ↔ rd = rs+rt,

sub rs, rt, rd ↔ rd = rs-rt,

and rs, rt, rd ↔ rd = rs&rt,

or rs, rt, rd ↔ rd = rs|rt,

slt rs, rt, rd,

```

## ALU for different instructions

- ▶ lw rt,  $0(rs) \leftrightarrow rt \leftarrow [rs+4*0]$ , add

- ▶ sw rt, x(rs)  $\leftrightarrow$  [rs+4 \* x]  $\leftarrow$  rt, add

- ▶ beq rs, rt, rd  $\leftrightarrow$  zero  $\leftarrow$  (rs-rt == 0) subtract

- ▶ add rs, rt, rd  $\leftrightarrow$  rd = rs+rt, add

- ▶ sub rs, rt, rd  $\leftrightarrow$  rd = rs-rt, sub

- ▶ and rs, rt, rd  $\leftrightarrow$  rd = rs & rt, and

- ightharpoonup or rs, rt, rd  $\leftrightarrow$  rd = rs rt, or

- ▶ slt rs, rt, rd, slt

|     | opcode | function |

|-----|--------|----------|

| lw  | 35     | -        |

| SW  | 43     | -        |

| beq | 4      | -        |

| add | 0      | 32       |

| sub | 0      | 34       |

| AND | 0      | 36       |

| OR  | 0      | 37       |

| slt | 0      | 42       |

| j   | 2      | -        |

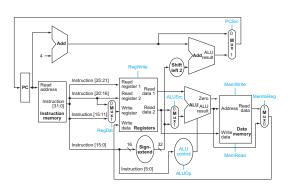

|     | Main ( | Control | function (Isb 6 bit from instruction) |                |                |       |       | ALU            | ALU Control |                       |       |       |       |

|-----|--------|---------|---------------------------------------|----------------|----------------|-------|-------|----------------|-------------|-----------------------|-------|-------|-------|

|     | ALUOP1 | ALUOP0  | F <sub>5</sub>                        | F <sub>4</sub> | F <sub>3</sub> | $F_2$ | $F_1$ | Ý <sub>0</sub> | operation   | <i>S</i> <sub>3</sub> | $S_2$ | $S_1$ | $S_0$ |

| lw  | 0      | 0       | ×                                     | ×              | ×              | ×     | ×     | ×              | add         | 0                     | 0     | 1     | 0     |

| sw  | 0      | 0       | ×                                     | ×              | ×              | ×     | ×     | ×              | add         | 0                     | 0     | 1     | 0     |

| beq | 0      | 1       | ×                                     | ×              | ×              | ×     | ×     | ×              | sub         | 0                     | 1     | 1     | 0     |

| add | 1      | ×       | 1                                     | 0              | 0              | 0     | 0     | 0              | add         | 0                     | 0     | 1     | 0     |

| sub | 1      | ×       | 1                                     | 0              | 0              | 0     | 1     | 0              | sub         | 0                     | 1     | 1     | 0     |

| AND | 1      | ×       | 1                                     | 0              | 0              | 1     | 0     | 0              | and         | 0                     | 0     | 0     | 0     |

| OR  | 1      | ×       | 1                                     | 0              | 0              | 1     | 0     | 1              | or          | 0                     | 0     | 0     | 1     |

| slt | 1      | ×       | 1                                     | 0              | 1              | 0     | 1     | 0              | slt         | 0                     | 1     | 1     | 1     |

|     | opcode | function |

|-----|--------|----------|

| lw  | 35     | -        |

| sw  | 43     | -        |

| beq | 4      | -        |

| add | 0      | 32       |

| sub | 0      | 34       |

| AND | 0      | 36       |

| OR  | 0      | 37       |

| slt | 0      | 42       |

| j   | 2      | -        |

|                       | ALU ( | ALU Control |           |          |  |  |  |  |

|-----------------------|-------|-------------|-----------|----------|--|--|--|--|

| <i>S</i> <sub>3</sub> | $S_2$ | $S_1$       | Operation |          |  |  |  |  |

| 0                     | 0     | 0           | 0         | AND      |  |  |  |  |

| 0                     | 0     | 0           | 1         | OR       |  |  |  |  |

| 0                     | 0     | 1           | 0         | ADD      |  |  |  |  |

| 0                     | 1     | 1           | 0         | SUBTRACT |  |  |  |  |

| 0                     | 1     | 1           | 1         | SLT      |  |  |  |  |

|     | Main ( | Control | function (Isb 6 bit from instruction) |                |                |       |       | ALU            | ALU Control |                       |       |       |       |

|-----|--------|---------|---------------------------------------|----------------|----------------|-------|-------|----------------|-------------|-----------------------|-------|-------|-------|

|     | ALUOP1 | ALUOP0  | F <sub>5</sub>                        | F <sub>4</sub> | F <sub>3</sub> | $F_2$ | $F_1$ | Ý <sub>0</sub> | operation   | <i>S</i> <sub>3</sub> | $S_2$ | $S_1$ | $S_0$ |

| lw  | 0      | 0       | ×                                     | ×              | ×              | ×     | ×     | ×              | add         | 0                     | 0     | 1     | 0     |

| sw  | 0      | 0       | ×                                     | ×              | ×              | ×     | ×     | ×              | add         | 0                     | 0     | 1     | 0     |

| beq | 0      | 1       | ×                                     | ×              | ×              | ×     | ×     | ×              | sub         | 0                     | 1     | 1     | 0     |

| add | 1      | ×       | 1                                     | 0              | 0              | 0     | 0     | 0              | add         | 0                     | 0     | 1     | 0     |

| sub | 1      | ×       | 1                                     | 0              | 0              | 0     | 1     | 0              | sub         | 0                     | 1     | 1     | 0     |

| AND | 1      | ×       | 1                                     | 0              | 0              | 1     | 0     | 0              | and         | 0                     | 0     | 0     | 0     |

| OR  | 1      | ×       | 1                                     | 0              | 0              | 1     | 0     | 1              | or          | 0                     | 0     | 0     | 1     |

| slt | 1      | ×       | 1                                     | 0              | 1              | 0     | 1     | 0              | slt         | 0                     | 1     | 1     | 1     |

|     | opcode | function |

|-----|--------|----------|

| lw  | 35     | -        |

| sw  | 43     | -        |

| beq | 4      | -        |

| add | 0      | 32       |

| sub | 0      | 34       |

| AND | 0      | 36       |

| OR  | 0      | 37       |

| slt | 0      | 42       |

| j   | 2      | -        |

|                       | ALU ( | Operation |       |           |  |

|-----------------------|-------|-----------|-------|-----------|--|

| <i>S</i> <sub>3</sub> | $S_2$ | $S_1$     | $S_0$ | Орегаціон |  |

| 0                     | 0     | 0         | 0     | AND       |  |

| 0                     | 0     | 0         | 1     | OR        |  |

| 0                     | 0     | 1         | 0     | ADD       |  |

| 0                     | 1     | 1         | 0     | SUBTRACT  |  |

| 0                     | 1     | 1         | 1     | SLT       |  |

|     | Main ( | Control | func  | ction (I       | sb 6 bit       | from i | nstruct | ion)           | ALU       | l                     | ALU ( | Control |       |

|-----|--------|---------|-------|----------------|----------------|--------|---------|----------------|-----------|-----------------------|-------|---------|-------|

|     | ALUOP1 | ALUOP0  | $F_5$ | F <sub>4</sub> | F <sub>3</sub> | $F_2$  | $F_1$   | Ý <sub>0</sub> | operation | <i>S</i> <sub>3</sub> | $S_2$ | $S_1$   | $S_0$ |

| lw  | 0      | 0       | ×     | ×              | ×              | ×      | ×       | ×              | add       | 0                     | 0     | 1       | 0     |

| sw  | 0      | 0       | ×     | ×              | ×              | ×      | ×       | ×              | add       | 0                     | 0     | 1       | 0     |

| beq | 0      | 1       | ×     | ×              | ×              | ×      | ×       | ×              | sub       | 0                     | 1     | 1       | 0     |

| add | 1      | ×       | 1     | 0              | 0              | 0      | 0       | 0              | add       | 0                     | 0     | 1       | 0     |

| sub | 1      | ×       | 1     | 0              | 0              | 0      | 1       | 0              | sub       | 0                     | 1     | 1       | 0     |

| AND | 1      | ×       | 1     | 0              | 0              | 1      | 0       | 0              | and       | 0                     | 0     | 0       | 0     |

| OR  | 1      | ×       | 1     | 0              | 0              | 1      | 0       | 1              | or        | 0                     | 0     | 0       | 1     |

| slt | 1      | ×       | 1     | 0              | 1              | 0      | 1       | 0              | slt       | 0                     | 1     | 1       | 1     |

|     | opcode | function |

|-----|--------|----------|

| lw  | 35     | -        |

| sw  | 43     | -        |

| beq | 4      | -        |

| add | 0      | 32       |

| sub | 0      | 34       |

| AND | 0      | 36       |

| OR  | 0      | 37       |

| slt | 0      | 42       |

| j   | 2      | -        |

|                       | ALU ( | Operation |       |           |  |

|-----------------------|-------|-----------|-------|-----------|--|

| <i>S</i> <sub>3</sub> | $S_2$ | $S_1$     | $S_0$ | Орегаціон |  |

| 0                     | 0     | 0         | 0     | AND       |  |

| 0                     | 0     | 0         | 1     | OR        |  |

| 0                     | 0     | 1         | 0     | ADD       |  |

| 0                     | 1     | 1         | 0     | SUBTRACT  |  |

| 0                     | 1     | 1         | 1     | SLT       |  |

|     | Main ( | Control | fund           | ction (I | sb 6 bit | from i | nstruct | ion)        | ALU       | 1              | ALU ( | Control |       |

|-----|--------|---------|----------------|----------|----------|--------|---------|-------------|-----------|----------------|-------|---------|-------|

|     | ALUOP1 | ALUOP0  | F <sub>5</sub> | $F_4$    | $F_3$    | $F_2$  | $F_1$   | $\dot{F}_0$ | operation | S <sub>3</sub> | $S_2$ | $S_1$   | $S_0$ |

| lw  | 0      | 0       | ×              | ×        | ×        | ×      | ×       | ×           | add       | 0              | 0     | 1       | 0     |

| sw  | 0      | 0       | ×              | ×        | ×        | ×      | ×       | ×           | add       | 0              | 0     | 1       | 0     |

| beq | 0      | 1       | ×              | ×        | ×        | ×      | ×       | ×           | sub       | 0              | 1     | 1       | 0     |

| add | 1      | ×       | 1              | 0        | 0        | 0      | 0       | 0           | add       | 0              | 0     | 1       | 0     |

| sub | 1      | ×       | 1              | 0        | 0        | 0      | 1       | 0           | sub       | 0              | 1     | 1       | 0     |

| AND | 1      | ×       | 1              | 0        | 0        | 1      | 0       | 0           | and       | 0              | 0     | 0       | 0     |

| OR  | 1      | ×       | 1              | 0        | 0        | 1      | 0       | 1           | or        | 0              | 0     | 0       | 1     |

| slt | 1      | ×       | 1              | 0        | 1        | 0      | 1       | 0           | slt       | 0              | 1     | 1       | 1     |

$S_3 = 0$ ,  $S_2 = ALUOP1'ALUOP0 + ALUOP1F_1$ ,  $S_2 = \cdots$

|     | opcode | function |

|-----|--------|----------|

| lw  | 35     | -        |

| sw  | 43     | -        |

| beq | 4      | -        |

| add | 0      | 32       |

| sub | 0      | 34       |

| AND | 0      | 36       |

| OR  | 0      | 37       |

| slt | 0      | 42       |

| j   | 2      | -        |

|                       | ALU (          | Operation |       |          |  |  |  |

|-----------------------|----------------|-----------|-------|----------|--|--|--|

| <i>S</i> <sub>3</sub> | S <sub>2</sub> | $S_1$     | $S_0$ |          |  |  |  |

| 0                     | 0              | 0         | 0     | AND      |  |  |  |

| 0                     | 0              | 0         | 1     | OR       |  |  |  |

| 0                     | 0              | 1         | 0     | ADD      |  |  |  |

| 0                     | 1              | 1         | 0     | SUBTRACT |  |  |  |

| 0                     | 1              | 1         | 1     | SLT      |  |  |  |

## i address

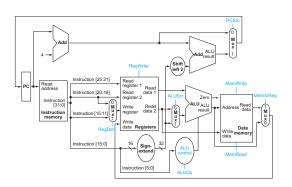

# j address

|   | Red | Jeg Regi | Wite All | SKC. | yc Net | Read Net | nvite ner | ntoRes | OR'S | OPO<br>Jump |

|---|-----|----------|----------|------|--------|----------|-----------|--------|------|-------------|

| j | Х   | Х        | Х        | Х    | Х      | Х        | Х         | Х      | Х    | 1           |

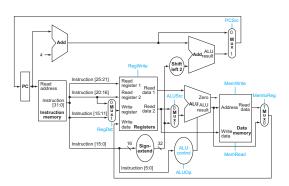

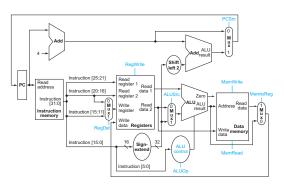

## Total Main Control Unit

|        |    | Reg | Det Ref | Write Nite | Si <sup>C</sup> C | yc Net | Read | nyrite ner | io Refe | OP'N | ORO .c  |

|--------|----|-----|---------|------------|-------------------|--------|------|------------|---------|------|---------|

|        |    | Seg | , Seg   | , br       | 80°               | " Ve   | Ne   | , Me       | , Mr    | , br | ) Jilui |

| R-type | 0  | 1   | 1       | 0          | 0                 | 0      | 0    | 0          | 1       | Х    | 0       |

| j      | 2  | X   | X       | X          | X                 | X      | X    | X          | X       | X    | 1       |

| beq    | 4  | X   | 0       | 0          | 1                 | 0      | 0    | X          | 0       | 1    | 0       |

| lw     | 35 | 0   | 1       | 1          | 0                 | 1      | 0    | 1          | 0       | 0    | 0       |

| SW     | 43 | X   | 0       | 1          | 0                 | 0      | 1    | X          | 0       | 0    | 0       |

## Total Main Control Unit

|        |    |     | Res | 2 <sup>3</sup>   | ₹0     |       |     |       |         |      |              |

|--------|----|-----|-----|------------------|--------|-------|-----|-------|---------|------|--------------|

|        |    | Reg | 666 | W. MI            | ی کرک  | y Ner | Mer | Write | nte All | PALL | OPO<br>Junio |

| R-type | 0  | 1   | 1   | 0                | 0      | 0     | 0   | 0     | 1       | Х    | 0            |

| j      | 2  | X   | X   | X                | Х      | X     | X   | X     | X       | X    | 1            |

| beq    | 4  | X   | 0   | 0                | 1      | 0     | 0   | X     | 0       | 1    | 0            |

| lw     | 35 | 0   | 1   | 1                | 0      | 1     | 0   | 1     | 0       | 0    | 0            |

| SW     | 43 | X   | 0   | 1                | 0      | 0     | 1   | X     | 0       | 0    | 0            |

|        |    |     |     | 2 <sup>6</sup> > | < 10 I | ROM   |     |       |         |      |              |